|

Xeon 5500/3500シリーズの紹介 (2009/6/1) |

Intel社は新しいアーキテクチャを採用したXeonプロセッサの新バージョン5500シリーズを3月31日に発表しました。弊社でもTS3Dシリーズに搭載して出荷を開始しています。以下では従来シリーズから大きく性能向上したXeon 5500シリーズについて簡単な紹介を行ないます。Xeon 3500シリーズも同時に発表されましたが、こちらは5500シリーズからQPIコネクション(後述)が一つ省かれて、シングルCPUとして使用されるCPUです。デスクトップ用CPUであるCore i7のメモリインターフェイスにECC機能が追加されたものと同等です。

Xeon 5500シリーズには、少数のコアで実行が行なわれる時には実行周波数が公称値よりも高くなるターボブースト機能(2.93GHz CPUの1コアだけを動かした場合3.33GHzで動作)が採用されたこと、CPU間・CPU-IO間をQuick Path Interconnectと呼ばれる通信線で結合したこと、キメ細かな省電力対策が施されたこと、4コアで共有された8MBのキャッシュメモリ等、多くの特筆すべき新しい技術が組み込まれていますが、Xeon 5500シリーズの性能向上を際立たせているのは、メモリへのアクセス速度が大幅に改善されたことです。

Xeon 5300、5400シリーズでは、2個のCPUは各々1チャンネル(10.5GB/sec)のバスによってチップセットに接続され、同じく1チャンネルのバス(21.3GB/sec)によってチップセットに接続されたメモリを共有していました。両CPUからのメモリアクセスはチップセットで調停されるため遅延が発生し、メモリバスの性能を低下させるきらいがありました。

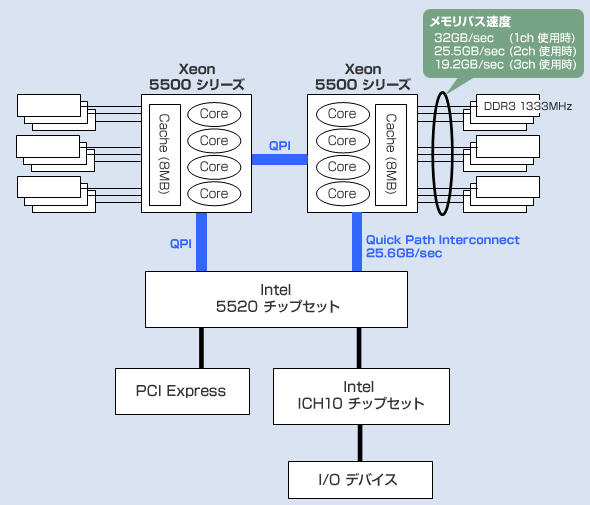

Xeon 5500シリーズでは、メモリ制御のためのチップセットが廃止され各々のCPUにメモリインターフェイス機能が内蔵されました。この結果メモリアクセスの遅延が小さくなっています。チップセットが行なっていたメモリ共有のために、高速(25.6GB/sec)なQuick Path Interconnect(QPI)で両CPUが接続され、相手方に接続されたメモリをアクセスすることが可能になっています。

また、バースト転送時のバンドレートが非常に高くなっています。Xeon 5500シリーズは3-wayインターリーブを行なうDDR3インターフェイスを3チャンネル有しています。DDR3 1333MHzメモリ3枚を1チャンネルだけに装備した時が最速で32GB/sec、2チャンネルに装備した時には25.5GB/sec、3チャンネルでは19.2GB/secとなります。2個のCPUによるコンピュータ全体のメモリアクセス速度はこの2倍の64GB/sec~38.4GB/secとなります。Xeon 5400シリーズのメモリアクセス速度は、先述のようにFSB 667MHzのCPUで21.3GB/sec、同800MHzで25.6GB/secでしたので、新シリーズになって大きく改善されています。

プログラムを実行した時のコンピュータの性能は、キャッシュを有効活用する効率的なプログラムではCPUの周波数に比例しますが、キャッシュミスヒットが多い一般的なプログラムでは、メモリアクセス速度に比例する傾向があります。Xeon新シリーズはメモリアクセス速度が大幅に向上したことにより、内蔵された4個の演算コアの性能を十分に発揮させることができるようになり、実性能が大きく向上しています。弊社のベンチマークのうち、「メモリアクセスの多発するプログラム」にその傾向が顕著に示されています。

Xeon 5500シリーズのブロック図